TUGAS PENDAHULUAN

MODUL 1

Gerbang Logika Dasar, Monostable Multivibrator & Flip

Percobaan 1

Kondisi 9 :

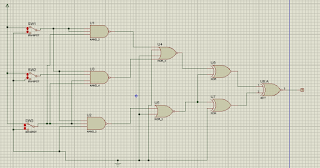

Buatlah sebuah rangkaian lengkap yang memuat 3 gerbang NAND dengan 3 input dan 4 input, kemudian gerbang NOR dengan 2 dan 4 input,kemudian 2 gerbang XOR dan 1 gerbang XNOR. Dan output akhir rangkaian keseluruhannya ditunjukkan dengan LED atau LOGIC PROBE. Dimana input awal berupa 3 saklar SPDT.

2. Komponen

1. Logicstate

2. Logicprobe

3. Gerbang NAND

4. Gerbang NOR

5. Gerbang XOR

6. Gerbang XNOR

7. SPDT

3. Gambar Rangkaian

4. Video Rangkaian

5. Prinsip Kerja

Pada rangkaian tersebut dapat dlihat bahwa kita memiliki beberapa gerbang logika yaitu, gerbang NAND, NOR, XOR dan XNOR. Pada rangkaian awal terdapat swith dengan tipe SPDT, jika dihubungkan dengan power maka akan berlogika 1 dan jika dihubungkan dengan ground akan berlogika 0.

Di rangkaian, pin yang berlogika 1 berlogika 1 dia akan menuju ke gerbang NAND U1 U2 U3, dilihat dari tabel kebenaran NAND bahwa apabila semua berlogika 1 maka menghasilkan logika 0 sedangkan apabila ada salah satu kaki input berlogika 1 ataupun nol maka akan berlogika 0.

Karena hal itu gerbang NAND U1 dan U3 bernilai nol karena dihubungi dengan pin dari saklar SPDT berlogika 1 yang berasal dari power dan gerbang NAND U2 berlogika 1 karena salah satu kakinya berlogika 0 yang berasal dari saklat SPDT yang dihubungi dengan ground. Selanjutnya, output dari gerbang NAND diumpankan ke gerbang NOR.

apabila semua kaki berlogika 0 maka menghasilkan input 1 dan apabila ada kaki berlogika 1 maka menghasilkan input 0, gerbang NOR U4 yang semua inputannya berlogika 0 menghasilkan output berlogika 1 dan NOR U5 inputannya berlogika 1 berasal dari output gerbang NAND dan berlogika 0 yang kaki inputan dihubungi dengan ground. MAka output dari gerbang NOR U5 berlogika 0.

Output dari gerbang NOR diunpankan ke gerbang XOR, yang apabila jumlah kaki input bernilai ganjil maka menghasilkan output berlogika 1 apabila jumlah inputan genap maka menghasilkan output berlogika 0, maka dari rangkaian diatas gerbang logika XOR U6 bernilai 1 serta U7 bernilai 0.

Output dari gerbang XOR diunpankan ke gerbang XNOR. Kebalikan dari XOR apabila jumlah inputan berjumlah ganjil maka output berlogika 0, sedangka jika jumlah inputan genap maka menghasilkan output berlogika 1

Gerbang nand

6. Link Download

0 komentar:

Posting Komentar